## PIC12Fxxx Instruction Set

Vojtěch Krmíček vojtec@ics.muni.cz

#### Instruction Set

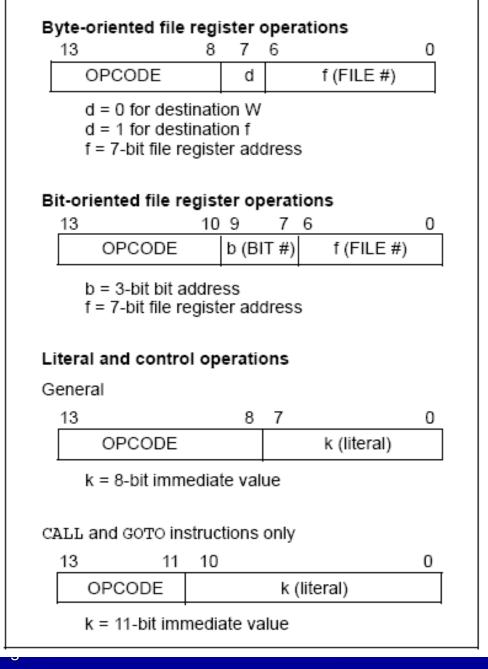

| Field | Description                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                |

| W     | Working register (accumulator)                                                                                                                                      |

| b     | Bit address within an 8-bit file register                                                                                                                           |

| k     | Literal field, constant data or label                                                                                                                               |

| х     | Don't care location (= 0 or 1). The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                       |

| PC    | Program Counter                                                                                                                                                     |

| TO    | Time-out bit                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                      |

## **Byte Operations**

| Mnemonic, |      | Donosintion.                 | Cycles  | 14-Bit Opcode |      |      | •    | Status   | Notes |

|-----------|------|------------------------------|---------|---------------|------|------|------|----------|-------|

| Opera     | nds  | Description                  |         | MSb           |      |      | LSb  | Affected | Notes |

|           |      | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIO         | NS   |      |      |          |       |

| ADDWF     | f, d | Add W and f                  | 1       | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d | AND W with f                 | 1       | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF      | f    | Clear f                      | 1       | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW      | -    | Clear W                      | 1       | 00            | 0001 | 0xxx | XXXX | Z        |       |

| COMF      | f, d | Complement f                 | 1       | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF      | f, d | Decrement f                  | 1       | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ    | f, d | Decrement f, Skip if 0       | 1(2)    | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF      | f, d | Increment f                  | 1       | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ    | f, d | Increment f, Skip if 0       | 1(2)    | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF     | f, d | Inclusive OR W with f        | 1       | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF      | f, d | Move f                       | 1       | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF     | f    | Move W to f                  | 1       | 00            | 0000 | lfff | ffff |          |       |

| NOP       | -    | No Operation                 | 1       | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF       | f, d | Rotate Left f through Carry  | 1       | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF       | f, d | Rotate Right f through Carry | 1       | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF     | f, d | Subtract W from f            | 1       | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d | Swap nibbles in f            | 1       | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF     | f, d | Exclusive OR W with f        | 1       | 00            | 0110 | dfff | ffff | Z        | 1,2   |

## **Bit Operations**

|                              | BIT-ORIENTED FILE REGISTER OPERATIONS |                                                                         |                        |                      |                                                  |              |  |                      |

|------------------------------|---------------------------------------|-------------------------------------------------------------------------|------------------------|----------------------|--------------------------------------------------|--------------|--|----------------------|

| BCF<br>BSF<br>BTFSC<br>BTFSS | f, b<br>f, b<br>f, b<br>f, b          | Bit Clear f Bit Set f Bit Test f, Skip if Clear Bit Test f, Skip if Set | 1<br>1<br>1(2)<br>1(2) | 01<br>01<br>01<br>01 | 00bb bfff<br>01bb bfff<br>10bb bfff<br>11bb bfff | ffff<br>ffff |  | 1,2<br>1,2<br>3<br>3 |

## **Literal and Control Operations**

|        | LITERAL AND CONTROL OPERATIONS |                             |   |    |           |      |        |  |

|--------|--------------------------------|-----------------------------|---|----|-----------|------|--------|--|

| ADDLW  | k                              | Add literal and W           | 1 | 11 | 111x kkkk | kkkk | C,DC,Z |  |

| ANDLW  | k                              | AND literal with W          | 1 | 11 | 1001 kkkk | kkkk | Z      |  |

| CALL   | k                              | Call subroutine             | 2 | 10 | 0kkk kkkk | kkkk |        |  |

| CLRWDT | -                              | Clear Watchdog Timer        | 1 | 00 | 0000 0110 | 0100 | TO,PD  |  |

| GOTO   | k                              | Go to address               | 2 | 10 | 1kkk kkkk | kkkk |        |  |

| IORLW  | k                              | Inclusive OR literal with W | 1 | 11 | 1000 kkkk | kkkk | Z      |  |

| MOVLW  | k                              | Move literal to W           | 1 | 11 | 00xx kkkk | kkkk |        |  |

| RETFIE | -                              | Return from interrupt       | 2 | 00 | 0000 0000 | 1001 |        |  |

| RETLW  | k                              | Return with literal in W    | 2 | 11 | 01xx kkkk | kkkk |        |  |

| RETURN | -                              | Return from Subroutine      | 2 | 00 | 0000 0000 | 1000 |        |  |

| SLEEP  | -                              | Go into Standby mode        | 1 | 00 | 0000 0110 | 0011 | TO,PD  |  |

| SUBLW  | k                              | Subtract W from literal     | 1 | 11 | 110x kkkk | kkkk | C,DC,Z |  |

| XORLW  | k                              | Exclusive OR literal with W | 1 | 11 | 1010 kkkk | kkkk | Z      |  |

# **Data Moving Operations**

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVLW k                                                                            |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                        |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |

| Operation:       | $(W) \to (f)$                              |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                        |

| Operation:       | $(f) \to (destination)$                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                         |

| Description:     | The contents of register f are moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register, since status flag Z is affected. |

#### Data Moving Operations (cont.)

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

## **Arithmetic Operations**

| ADDLW            | Add Literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \to (W)$                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| ADDWF            | Add W and f                                                                                                                                                        |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |  |  |  |

| Operation:       | $(W) + (f) \to (destination)$                                                                                                                                      |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                           |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                           |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [label] SUBWF f,d                                                                                                                                                           |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |

| Operation:          | $(f) - (W) \rightarrow (destination)$                                                                                                                                       |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                    |

| Description:        | Subtract (2's complement method) W register from register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

2.3.2010 PB171 Spri

#### **Arithmetic perations (cont.)**

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                            |

| Operation:       | $(f) - 1 \rightarrow (destination)$                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | $(f) + 1 \rightarrow (destination)$                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

# **Logic Operations**

| ANDLW            | AND Literal with W                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) \ .AND. \ (k) \to (W)$                                                                                   |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] ANDWF f,d                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | $(W) \ .AND. \ (f) \to (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | $(W) \ .OR. \ k \to (W)$                                                                                         |

| Status Affected: | Z                                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| IORWF            | Inclusive OR W with f                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |

| Operation:       | $(W) \ .OR. \ (f) \to (destination)$                                                                                                                        |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

#### **Logic Operations (cont.)**

| XORLW            | Exclusive OR Literal with W                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                 |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| COMF             | Complement f                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                             |

| Operation:       | $(\overline{f}) 	o (\text{destination})$                                                                                                       |

| Status Affected: | Z                                                                                                                                              |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] XORWF f,d                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |

| Operation:       | $(W) \ .XOR. \ (f) \to (destination)$                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

## **Rotation Operations**

| RLF              | Rotate Left f through Carry                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                          |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                |

| Operation:       | See description below                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is stored back in register 'f'. |

|                  | Tregister 1                                                                                                                                                                                       |

| RRF            | Rotate Right f through Carry                                                                                                                                                                       |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:        | [ <i>label</i> ] RRF f,d                                                                                                                                                                           |

| Operands:      | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                 |

| Operation:     | See description below                                                                                                                                                                              |

| Status Affecto | ed: C                                                                                                                                                                                              |

| Description:   | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

|                | C Register f                                                                                                                                                                                       |

## **Conditional Jumps**

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                             |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2Tcy instruction. |

|                  |                                                                                                                                                                                                |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] BTFSC f,b                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                          |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                             |

| Operation:       | (f) + 1 → (destination),<br>skip if result = 0                                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead, making it a 2TCY instruction. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2Tcy instruction. |

## **Unconditional Jumps**

| GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] GOTO k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $\begin{array}{l} k \rightarrow PC < 10:0 > \\ PCLATH < 4:3 > \rightarrow PC < 12:11 > \end{array}$                                                                               |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |

| CALL             | Call Subroutine                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS, k $\rightarrow$ PC<10:0>, (PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two-cycle instruction. |

#### Returns

| RETURN           | Return from Subroutine                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                 |

| Operands:        | None                                                                                                                                           |

| Operation:       | $TOS \to PC$                                                                                                                                   |

| Status Affected: | None                                                                                                                                           |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction. |

| RETLW            | Return with Literal in W                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETLW k                                                                                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |

| Operation:       | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow PC \end{array}$                                                                                                 |

| Status Affected: | None                                                                                                                                                                    |

| Description:     | The W register is loaded with the eight-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |

| RETFIE           | Return from Interrupt                      |

|------------------|--------------------------------------------|

| Syntax:          | [label] RETFIE                             |

| Operands:        | None                                       |

| Operation:       | $TOS \rightarrow PC$ , $1 \rightarrow GIE$ |

| Status Affected: | None                                       |

#### Other Instructions

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| CLRWDT           | Clear Watchdog Timer                                                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                        |

| Operands:        | None                                                                                                                  |

| Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{\text{TO}}$<br>1 → $\overline{\text{PD}}$                           |

| Status Affected: | TO, PD                                                                                                                |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. STATUS bits TO and PD are set. |

#### **SLEEP** [label] SLEEP Syntax: Operands: None Operation: $00h \rightarrow WDT$ , $0 \rightarrow WDT$ prescaler, $1 \rightarrow \overline{TO}$ , $0 \rightarrow \overline{PD}$ TO, PD Status Affected: Description: The power-down STATUS bit, PD is cleared. Time-out STATUS bit, TO is set. Watchdog Timer and its prescaler are cleared. The processor is put into SLEEP

mode with the oscillator stopped.