# A/D Converter and Comparator

PIC 12F675

#### A/D Converter

Conversion of an analog input signal to a 10bit binary representation of that signal

► PIC 12F675 has 4 ADC (multiplexed)

Generates interrupt (ADIF)

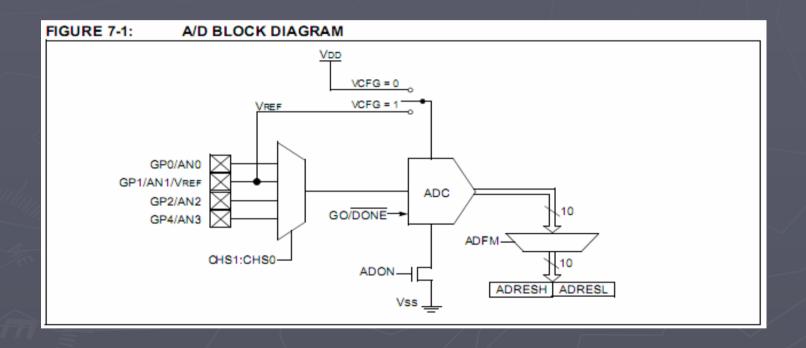

# A/D block diagram

#### A/D - ANSEL

#### REGISTER 7-2: ANSEL — ANALOG SELECT REGISTER (ADDRESS: 9Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | ADCS2 | ADCS1 | ADCS0 | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 Unimplemented: Read as '0'.

bit 6-4 ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2 001 = Fosc/8 010 = Fosc/32

010 = FOSC/32

x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)

100 = Fosc/4 101 = Fosc/16 110 = Fosc/64

bit 3-0 ANS3:ANS0: Analog Select bits

(Between analog or digital function on pins AN<3:0>, respectively.)

1 = Analog input; pin is assigned as analog input<sup>(1)</sup>

0 = Digital I/O; pin is assigned to port or special function

Note 1: Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change. The corresponding TRISIO bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| urce (TAD)            | Device Frequency                              |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operation ADCS2:ADCS0 |                                               | 5 MHz                                                                                                                                                                                   | 4 MHz                                                                                                                                                                                                                                                                                                                                 | 1.25 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 000                   | 100 ns <sup>(2)</sup>                         | 400 ns <sup>(2)</sup>                                                                                                                                                                   | 500 ns <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                 | 1.6 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 100                   | 200 ns <sup>(2)</sup>                         | 800 ns <sup>(2)</sup>                                                                                                                                                                   | 1.0 μs <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                 | 3.2 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 001                   | 400 ns <sup>(2)</sup>                         | 1.6 µs                                                                                                                                                                                  | 2.0 μs                                                                                                                                                                                                                                                                                                                                | 6.4 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 101                   | 800 ns <sup>(2)</sup>                         | 3.2 µs                                                                                                                                                                                  | 4.0 μs                                                                                                                                                                                                                                                                                                                                | 12.8 μs <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 010                   | 1.6 µs                                        | 6.4 μs                                                                                                                                                                                  | 8.0 μs <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                 | 25.6 μs <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 110                   | 3.2 μs                                        | 12.8 μs <sup>(3)</sup>                                                                                                                                                                  | 16.0 μs <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                | 51.2 μs <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| x11                   | 2 - 6 μs <sup>(1,4)</sup>                     | 2 - 6 μs <sup>(1,4)</sup>                                                                                                                                                               | 2 - 6 μs <sup>(1,4)</sup>                                                                                                                                                                                                                                                                                                             | 2 - 6 μs <sup>(1,4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| _                     | 000<br>000<br>100<br>001<br>101<br>010<br>110 | OCS2:ADCS0     20 MHz       000     100 ns <sup>(2)</sup> 100     200 ns <sup>(2)</sup> 001     400 ns <sup>(2)</sup> 101     800 ns <sup>(2)</sup> 010     1.6 μs       110     3.2 μs | OCS2:ADCS0         20 MHz         5 MHz           000         100 ns(2)         400 ns(2)           100         200 ns(2)         800 ns(2)           001         400 ns(2)         1.6 μs           101         800 ns(2)         3.2 μs           010         1.6 μs         6.4 μs           110         3.2 μs         12.8 μs(3) | OCS2:ADCS0         20 MHz         5 MHz         4 MHz           000         100 ns <sup>(2)</sup> 400 ns <sup>(2)</sup> 500 ns <sup>(2)</sup> 100         200 ns <sup>(2)</sup> 800 ns <sup>(2)</sup> 1.0 μs <sup>(2)</sup> 001         400 ns <sup>(2)</sup> 1.6 μs         2.0 μs           101         800 ns <sup>(2)</sup> 3.2 μs         4.0 μs           010         1.6 μs         6.4 μs         8.0 μs <sup>(3)</sup> 110         3.2 μs         12.8 μs <sup>(3)</sup> 16.0 μs <sup>(3)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The A/D RC source has a typical TAD time of 4 μs for VDD > 3.0V.

- These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

# A/D - ADCONO

|               |                                                                                                                                    |                                           |           | /            |       |       | \              |       |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------|--------------|-------|-------|----------------|-------|--|--|

| REGISTER 7-1: | STER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)                                                                             |                                           |           |              |       |       |                |       |  |  |

|               | R/W-0                                                                                                                              | R/W-0                                     | U-0       | U-0          | R/W-0 | R/W-0 | R/W-0          | R/W-0 |  |  |

|               | ADFM VCFG CHS1 CHS0 GO/DONE ADOI                                                                                                   |                                           |           |              |       |       |                |       |  |  |

|               | bit 7 bit 0                                                                                                                        |                                           |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    |                                           |           |              |       |       |                |       |  |  |

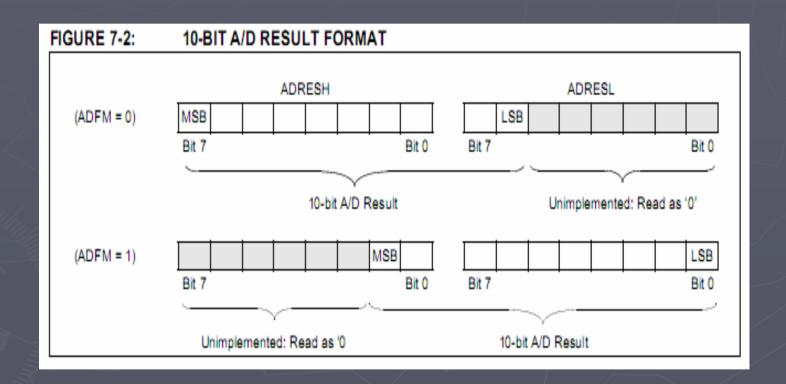

| bit 7         | ADFM: A/D Result Formed Select bit                                                                                                 |                                           |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    | 1 = Right justified<br>0 = Left justified |           |              |       |       |                |       |  |  |

| bit 6         |                                                                                                                                    | tage Refere                               | nce hit   |              |       |       |                |       |  |  |

| Dit 0         | 1 = VREF p                                                                                                                         | •                                         | nice bit  |              |       |       |                |       |  |  |

|               | 0 = VDD                                                                                                                            |                                           |           |              |       |       |                |       |  |  |

| bit 5-4       | Unimplem                                                                                                                           | ented: Rea                                | d as zero |              |       |       |                |       |  |  |

| bit 3-2       | CHS1:CHS0: Analog Channel Select bits                                                                                              |                                           |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    | nel 00 (AN0<br>nel 01 (AN1                |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    | nel 02 (AN2                               |           |              |       |       |                |       |  |  |

|               | 11 = Channel 03 (AN3)                                                                                                              |                                           |           |              |       |       |                |       |  |  |

| bit 1         | GO/DONE: A/D Conversion Status bit                                                                                                 |                                           |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    |                                           |           |              |       |       | nversion cycle |       |  |  |

|               | This bit is automatically cleared by hardware when the A/D conversion has completed.  0 = A/D conversion completed/not in progress |                                           |           |              |       |       |                |       |  |  |

| bit 0         | ADON: A/D Conversion STATUS bit                                                                                                    |                                           |           |              |       |       |                |       |  |  |

|               | 1 = A/D converter module is operating                                                                                              |                                           |           |              |       |       |                |       |  |  |

|               | 0 = A/D converter is shut-off and consumes no operating current                                                                    |                                           |           |              |       |       |                |       |  |  |

|               |                                                                                                                                    |                                           |           |              |       |       |                |       |  |  |

|               | Legend:  R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                      |                                           |           |              |       |       |                |       |  |  |

|               | R = Reada                                                                                                                          |                                           |           | /ritable bit |       | •     |                |       |  |  |

|               | - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                        |                                           |           |              |       |       |                |       |  |  |

# A/D – output registers

# A/D – example (without INT)

```

//A/D init

//ADCS2 ADCS1 ADCS0 ANS3 ANS2 ANS1 ANS0

ANSEL=0b1100001;

//ADFM VCFG - CHS1 CHS0 GO/DONE ADON

ADCON0=0b00000000;

ADON=1; //ENABLE A/D convertor

GODONE=1; //start

if (GODONE==0) {data=ADRESH;} //data rdy

```

#### Comparator

- The PIC12F629/675 devices have one analog comparator

- Compare two analog values

- On GP0 and GP1 are inputs to the comparator

- ► GP2 can be the comparator output

- Generates interrupt (CMIF)

# Comparator - CMCON

|               |                                                                            |                             |          |             |           | \         |                |       |  |

|---------------|----------------------------------------------------------------------------|-----------------------------|----------|-------------|-----------|-----------|----------------|-------|--|

| REGISTER 6-1: | CMCON -                                                                    | - COMPAR                    | RATOR CO | NTROL R     | EGISTER ( | ADDRESS   | S: 19h)        |       |  |

|               | U-0                                                                        | R-0                         | U-0      | R/W-0       | R/W-0     | R/W-0     | R/W-0          | R/W-0 |  |

|               | - COUT - CINV CIS CM2 CM1 C                                                |                             |          |             |           |           |                |       |  |

|               | bit 7                                                                      |                             |          |             |           |           |                |       |  |

| bit 7         | Unimplemented: Read as '0'                                                 |                             |          |             |           |           |                |       |  |

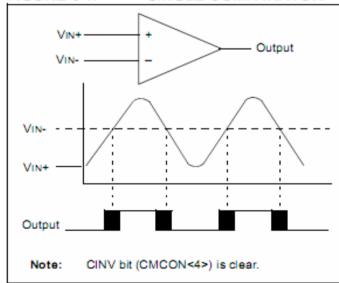

| bit 6         |                                                                            | COUT: Comparator Output bit |          |             |           |           |                |       |  |

| 511.0         | When CIN\                                                                  | •                           | tput bit |             |           |           |                |       |  |

|               | 1 = VIN+ >                                                                 |                             |          |             |           |           |                |       |  |

|               | 0 = VIN+ <                                                                 |                             |          |             |           |           |                |       |  |

|               | When CIN\ 1 = VIN+ <                                                       |                             |          |             |           |           |                |       |  |

|               | 0 = VIN+ >                                                                 |                             |          |             |           |           |                |       |  |

| bit 5         | Unimplemented: Read as '0'                                                 |                             |          |             |           |           |                |       |  |

| bit 4         | CINV: Comparator Output Inversion bit                                      |                             |          |             |           |           |                |       |  |

|               | 1 = Output inverted 0 = Output not inverted                                |                             |          |             |           |           |                |       |  |

| hii 0         | •                                                                          |                             |          |             |           |           |                |       |  |

| bit 3         |                                                                            | arator Input<br>:CM0 = 110  |          |             |           |           |                |       |  |

|               |                                                                            | nnects to Cl                |          |             |           |           |                |       |  |

|               | 0 = VIN- cor                                                               | 0 = Vin- connects to CIN-   |          |             |           |           |                |       |  |

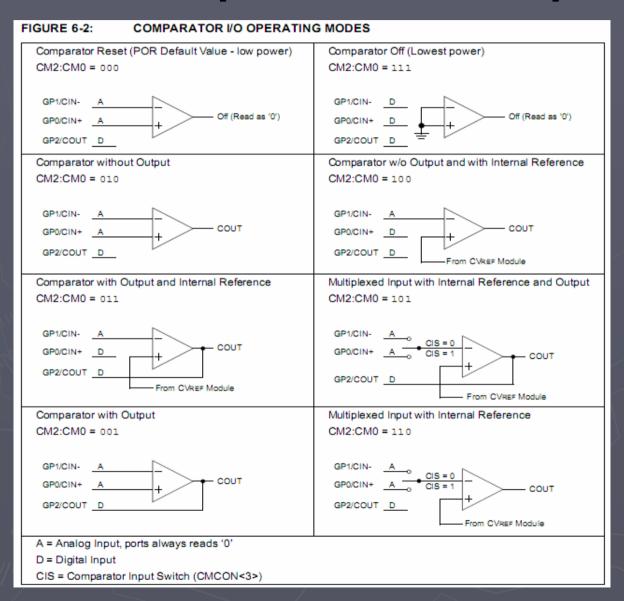

| bit 2-0       |                                                                            | Comparato                   |          |             |           |           |                |       |  |

|               | Figure 6-2 shows the Comparator modes and CM2:CM0 bit settings             |                             |          |             |           |           |                |       |  |

|               |                                                                            |                             |          |             |           |           |                |       |  |

|               | Legend:                                                                    |                             |          |             |           |           |                |       |  |

|               | R = Readal                                                                 | ole bit                     | W = W    | ritable bit | U = Unim  | plemented | bit, read as ' | 0.    |  |

|               | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                             |          |             |           |           |                |       |  |

#### Comparator – operation modes

TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

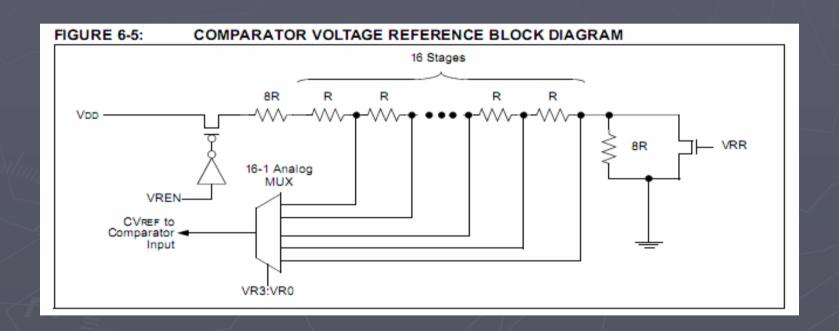

### Comparator – voltage reference

► The voltage reference can output 32 distinct voltage levels

| REGISTER 6-2: | VRCON — VOLTAGE REFERENCE CONTROL REGISTER (ADDRESS: 99h)                                                                                                                    |   |     |   |     |     |     |     |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|-----|-----|-----|-----|--|--|

|               | R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                                                      |   |     |   |     |     |     |     |  |  |

|               | VREN                                                                                                                                                                         | _ | VRR | _ | VR3 | VR2 | VR1 | VR0 |  |  |

|               | bit 7 bit 0                                                                                                                                                                  |   |     |   |     |     |     |     |  |  |

| bit 7         | VREN: CVREF Enable bit  1 = CVREF circuit powered on  0 = CVREF circuit powered down, no IDD drain                                                                           |   |     |   |     |     |     |     |  |  |

| bit 6         | Unimplemented: Read as '0'                                                                                                                                                   |   |     |   |     |     |     |     |  |  |

| bit 5         | VRR: CVREF Range Selection bit<br>1 = Low range<br>0 = High range                                                                                                            |   |     |   |     |     |     |     |  |  |

| bit 4         | Unimplemented: Read as '0'  VR3:VR0: CVREF value selection 0 ≤ VR [3:0] ≤ 15  When VRR = 1: CVREF = (VR3:VR0 / 24) * VDD  When VRR = 0: CVREF = VDD/4 + (VR3:VR0 / 32) * VDD |   |     |   |     |     |     |     |  |  |

| bit 3-0       |                                                                                                                                                                              |   |     |   |     |     |     |     |  |  |

|               | Legend:                                                                                                                                                                      |   |     |   |     |     |     |     |  |  |

|               | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                         |   |     |   |     |     |     |     |  |  |

|               | - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                  |   |     |   |     |     |     |     |  |  |

# Comparator – voltage reference

## Comparator - example

```

//init

// - COUT - CINV CIS CM2 CM1 CM0

CMCON=0;

output=COUT;

```

#### References

Source:

http://ww1.microchip.com/downloads/en/devicedoc/41190c.pdf