# PV200 Introduction to hardware description languages

Week 02: Combination logic - Schematic, basic gates

Ing. Jiří Čulen, 5.10.2021

# **Agenda**

- 1. New empty project in the Quartus

- 2. Schematic editor

- 3. I/O settings

- 4. Programming the device

- 5. Half adder

- 6. Ful adder

- 7. Adding of two bits number

#### New empty project in the Quartus

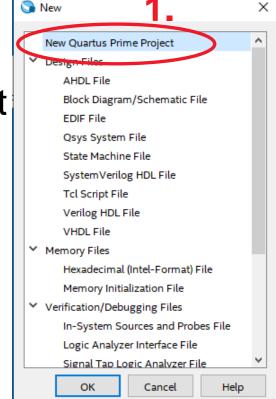

File -> New ->New Quartus Prime Project

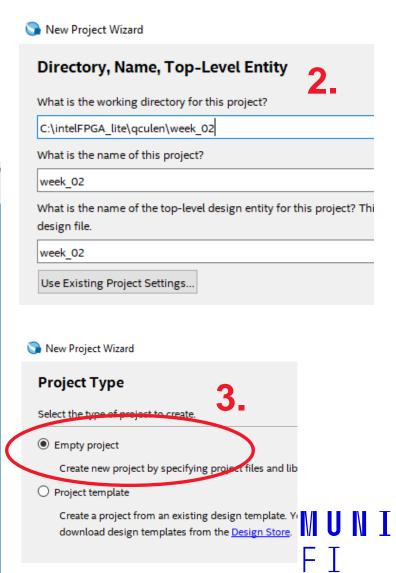

Select working directory and name of the

project

Define name of the project

Project type – Empty project

– Skip add files

## New empty project in the Quartus

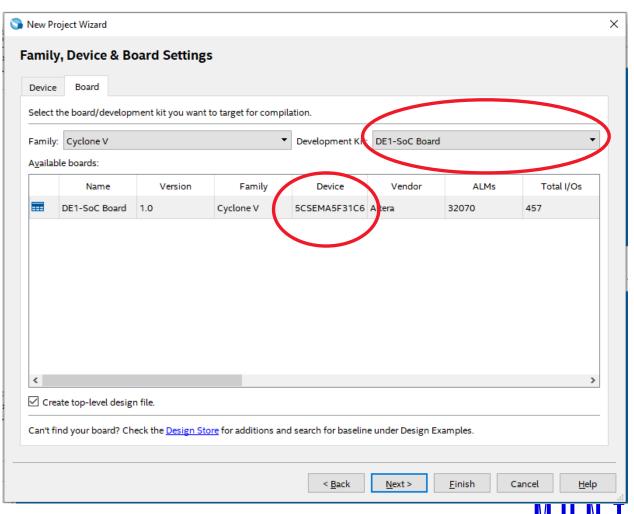

- Select device from the Board DE1-SoC or manually 5CSEMA5F31C6

- Skip EDA Tool Settings

- Finish

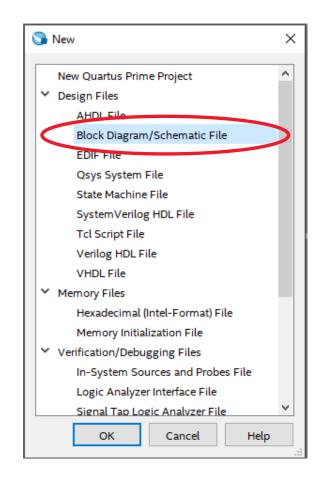

## New empty project in the Quartus

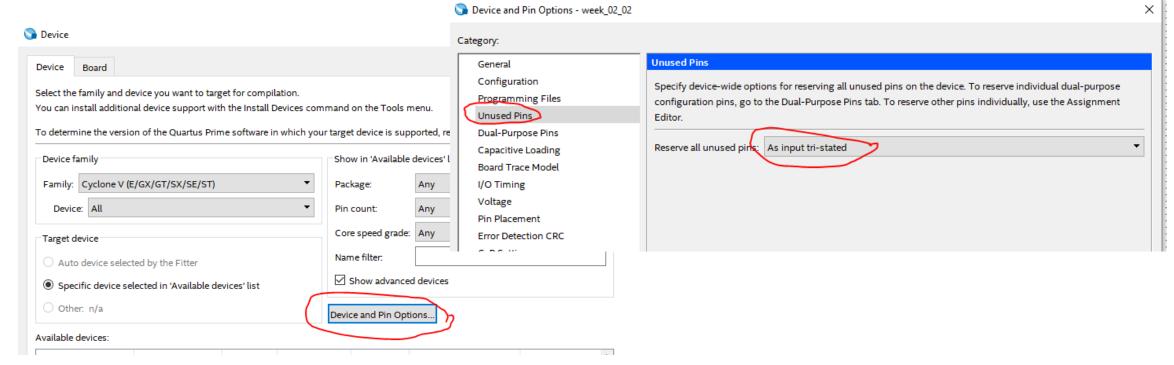

– Assignment -> Device -> Device and Pin Options

Unused Pins -> As input tri-stated

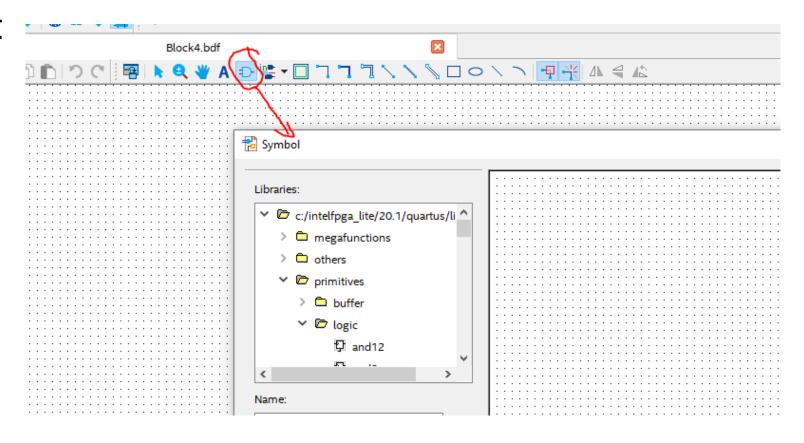

File -> New -> Block Diagram/Schematic File

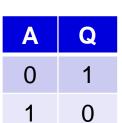

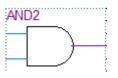

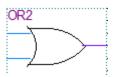

#### — We will need four basic gates

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

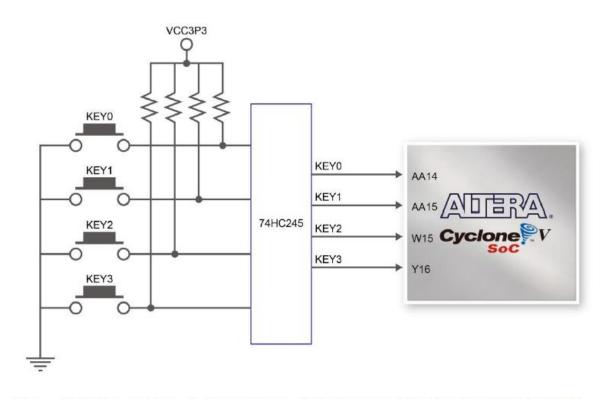

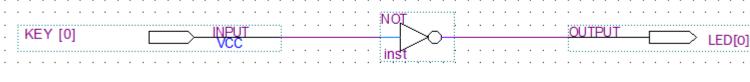

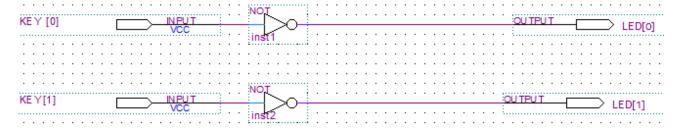

We will use keys from the board, which are in negative logic. We need to invert it for positive logic.

Figure 3-14 Connections between the push-buttons and the Cyclone V SoC FPGA

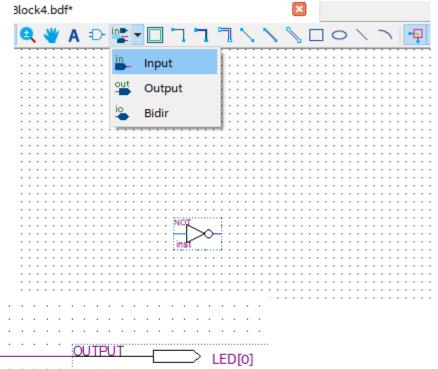

-Place a symbol not

- Place one input port and one output port and connect it to the NOT gate.

- -The name of the input port will KEY[0], of the output LED[0].

- -Save the schematic file.

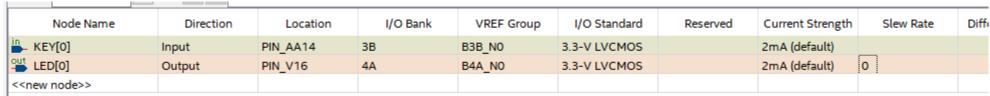

# I/O settings

Assignment of keys from the DE1-SoC manual

Table 3-7 Pin Assignment of Push-buttons

| Signal Name | FPGA Pin No. | Description    | I/O Standard |  |

|-------------|--------------|----------------|--------------|--|

| KEY[0]      | PIN_AA14     | Push-button[0] | 3.3V         |  |

| KEY[1]      | PIN_AA15     | Push-button[1] | 3.3V         |  |

| KEY[2]      | PIN_W15      | Push-button[2] | 3.3V         |  |

| KEY[3]      | PIN_Y16      | Push-button[3] | 3.3V         |  |

# I/O settings

#### – Assignment of LEDS from the DE1-SoC manual

Table 3-8 Pin Assignment of LEDs

| Signal Name | FPGA Pin No. | Description | I/O Standard |

|-------------|--------------|-------------|--------------|

| LEDR[0]     | PIN_V16      | LED [0]     | 3.3V         |

| LEDR[1]     | PIN_W16      | LED [1]     | 3.3V         |

| LEDR[2]     | PIN_V17      | LED [2]     | 3.3V         |

| LEDR[3]     | PIN_V18      | LED [3]     | 3.3V         |

| LEDR[4]     | PIN_W17      | LED [4]     | 3.3V         |

| LEDR[5]     | PIN_W19      | LED [5]     | 3.3V         |

| LEDR[6]     | PIN_Y19      | LED [6]     | 3.3V         |

| LEDR[7]     | PIN_W20      | LED [7]     | 3.3V         |

| LEDR[8]     | PIN_W21      | LED [8]     | 3.3V         |

| LEDR[9]     | PIN_Y21      | LED [9]     | 3.3V         |

# I/O settings

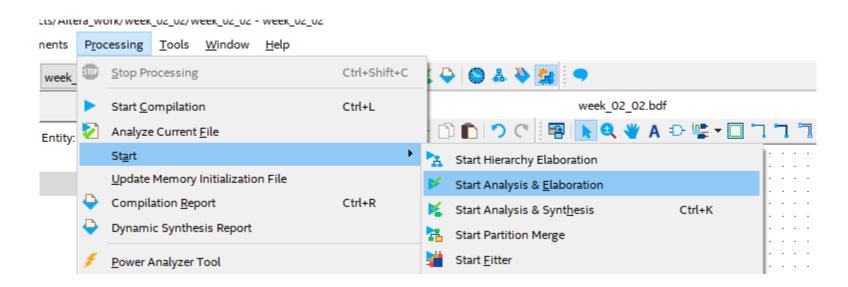

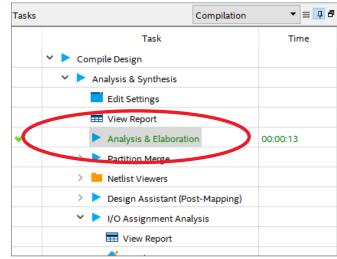

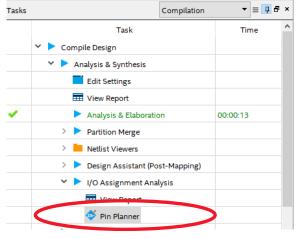

#### Processing -> Start -> Start Analysis & Elaboration

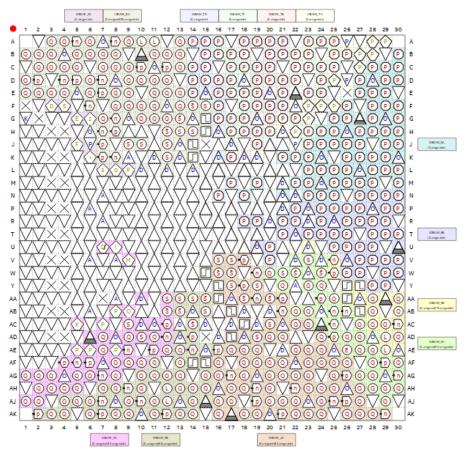

#### Top View - Wire Bond Cyclone V - 5CSEMA5F31C6

# I/O settings

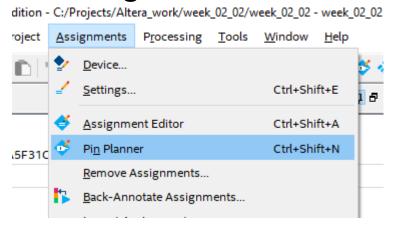

– Assignments -> Pin Planner

#### Set the right parameters for our pins

- Compile the project

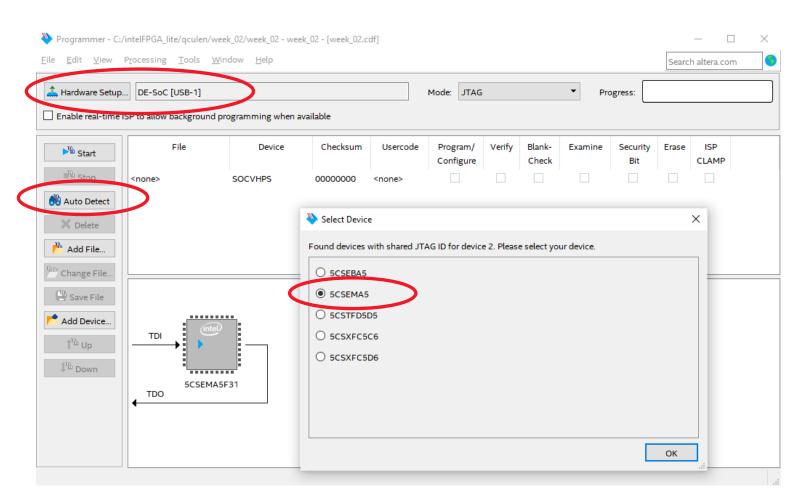

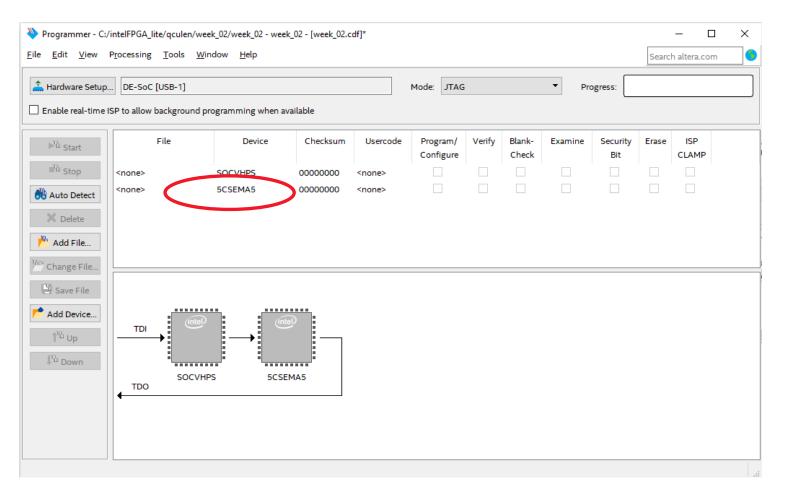

- Open the programmer

- Check connection to the DE SoC board

- Select 5CSEMA5

- Detect your FPGA

- FPGA 5CSEMA5 is detected

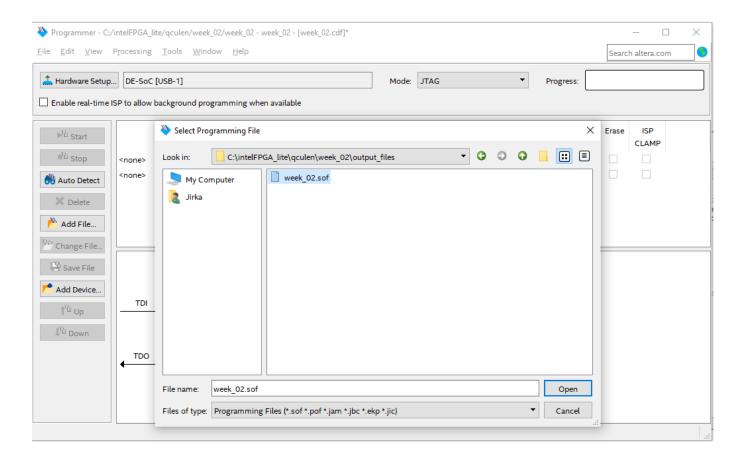

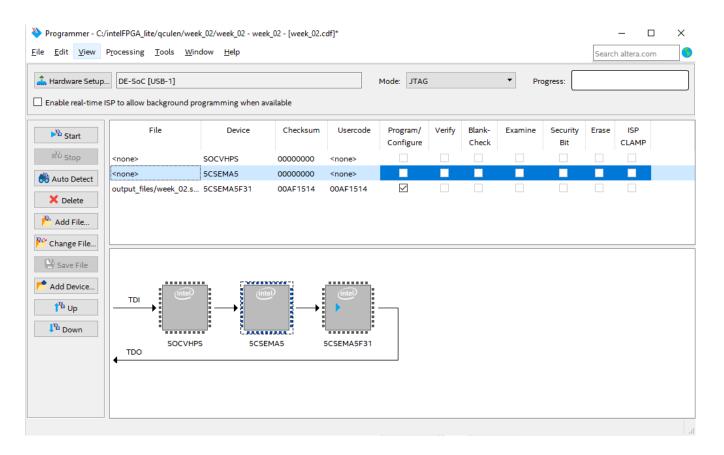

– Add file to the 5CSEMA5 device from the project

– Delete device 5CSEMA5

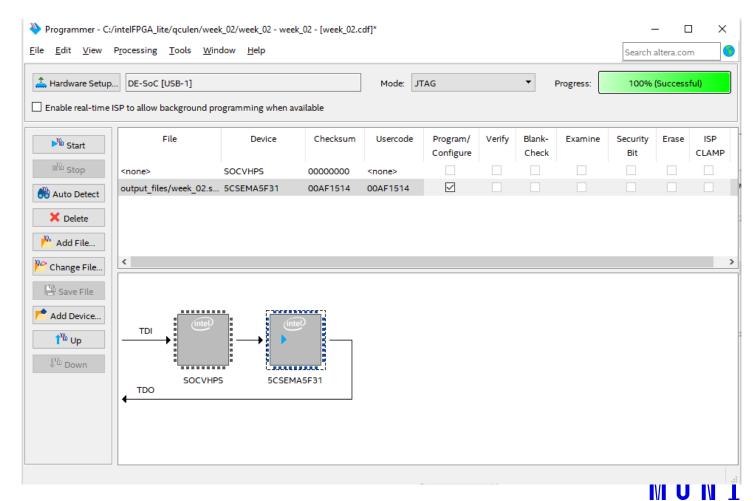

- Select 5CSEMA5F31

- Start the programming

- Test your application

#### Half adder

- Add the next pair of KEY and LED.

- For loading new ports to the I/O planner, You need repeat start of the Analysis & Elaboration

- Compile it and test it.

| Node Name  | Direction | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard | Reserved | Current Strength | Slew Rate |

|------------|-----------|----------|----------|------------|-----------------|--------------|----------|------------------|-----------|

| in_ KEY[1] | Input     | PIN_AA15 | 3B       | B3B_N0     | PIN_AA15        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[0] | Input     | PIN_AA14 | 3B       | B3B_N0     | PIN_AA14        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| out LED[1] | Output    | PIN_W16  | 4A       | B4A_N0     | PIN_W16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

| Cut LED[0] | Output    | PIN_V16  | 4A       | B4A_N0     | PIN_V16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

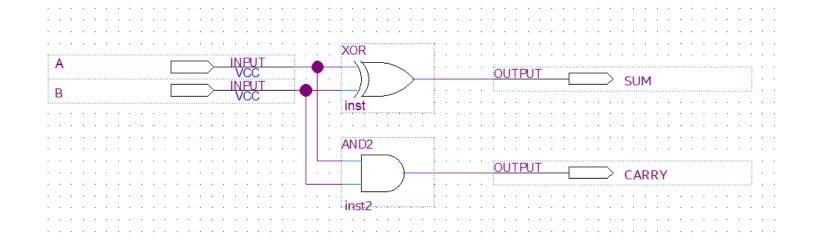

#### Half adder

- Create a new schematic file "half\_adder"

- Use File -> Create/Update -> Create Symbol Files for Current File

| Α | В | SUM | CARRY |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 1 | 0 | 1   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 1 | 0   | 1     |

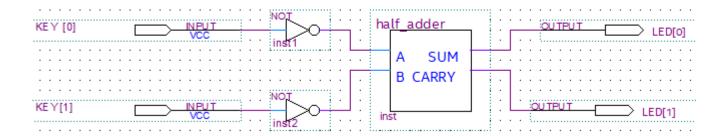

#### Half adder

- Put the half adder to the top schematic

- Compile it, program it, and test it...

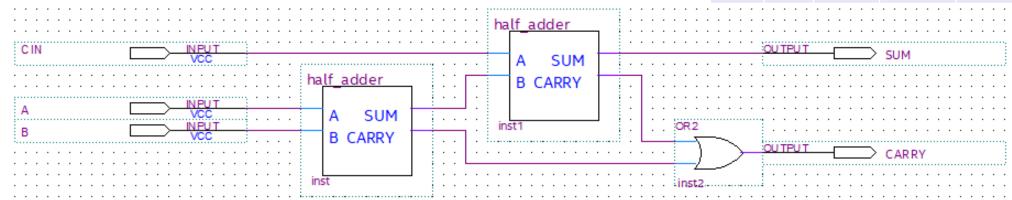

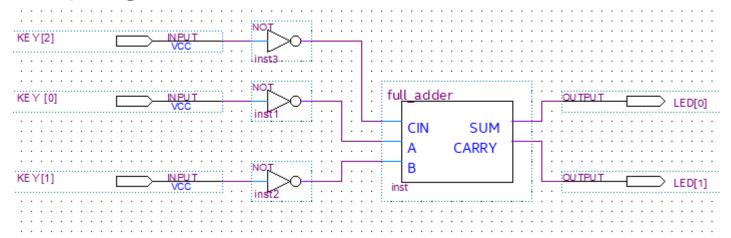

#### Full adder

- We can build full adder by using of half adders or by many others way...

- Create the new schematic file "full\_adder", and create symbol files

| A | В | CIN | SUM | CARRY |

|---|---|-----|-----|-------|

| 0 | 0 | 0   | 0   | 0     |

| 1 | 0 | 0   | 1   | 0     |

| 0 | 1 | 0   | 1   | 0     |

| 1 | 1 | 0   | 0   | 1     |

| 0 | 0 | 1   | 1   | 0     |

| 1 | 0 | 1   | 0   | 1     |

| 0 | 1 | 1   | 0   | 1     |

| 1 | 1 | 1   | 1   | 1     |

#### Full adder

- Put the half adder to the top schematic

- Compile it, program it, and test it...

| Node Name  | Direction | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard | Reserved | Current Strength | Slew Rate |

|------------|-----------|----------|----------|------------|-----------------|--------------|----------|------------------|-----------|

| KEY[2]     | Input     | PIN_W15  | 3B       | B3B_N0     | PIN_W15         | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[1] | Input     | PIN_AA15 | 3B       | B3B_N0     | PIN_AA15        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[0] | Input     | PIN_AA14 | 3B       | B3B_N0     | PIN_AA14        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| out LED[1] | Output    | PIN_W16  | 4A       | B4A_N0     | PIN_W16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

| LED[0]     | Output    | PIN_V16  | 4A       | B4A_N0     | PIN_V16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

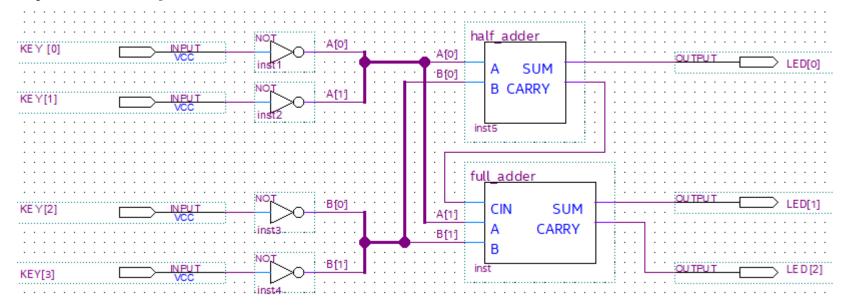

# Adding of two bits number

– Modify the top schema and test it

| Node Name  | Direction | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard | Reserved | Current Strength | Slew Rate |

|------------|-----------|----------|----------|------------|-----------------|--------------|----------|------------------|-----------|

| in_ KEY[3] | Input     | PIN_Y16  | 3B       | B3B_N0     | PIN_Y16         | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[2] | Input     | PIN_W15  | 3B       | B3B_N0     | PIN_W15         | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[1] | Input     | PIN_AA15 | 3B       | B3B_N0     | PIN_AA15        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| in_ KEY[0] | Input     | PIN_AA14 | 3B       | B3B_N0     | PIN_AA14        | 3.3-V LVCMOS |          | 2mA (default)    |           |

| out LED[2] | Output    | PIN_V17  | 4A       | B4A_N0     | PIN_V17         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

| Cut LED[1] | Output    | PIN_W16  | 4A       | B4A_N0     | PIN_W16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

| LED[0]     | Output    | PIN_V16  | 4A       | B4A_N0     | PIN_V16         | 3.3-V LVCMOS |          | 2mA (default)    | 0         |

# Thank you for attention

Ing. Jiří Čulen jiri.culen@mail.muni.cz